# PARALLEL PROCESSING USING TRANSPUTERS Spring 1997

Prepared By: Tarak Modi Advisor: Dr. Wells

# TRANSPUTERS: HARDWARE DESCRIPTION

# A Brief Background

The transputer was introduced to the world in 1985 by INMOS limited. The transputer was a VLSI chip, and at that time was heralded as a revolution in the world of computing. The transputer is essentially a high performance microprocessor. One of its most significant features is its ability to perform multitasking in hardware, and its sub micro-second context switching. Context switch time denotes the time it takes for a higher priority task to preempt a lower priority task, and start executing. Communication between processes is also provided by hardware, both for internal data transfers, and transfers between different processors.

The first processor in the transputer series was T414 and boasted an unprecedented speed of 10 MIPS (millions of instructions per second), with the capability of multitasking in hardware. Dedicated on chip link controllers allowed for communications between processes running on different processors (transputers), with a minimal processor overhead. The T414 is a 32-bit processor with 2K on-chip RAM and four interprocessor links, capable of addressing upto 4Gbytes of external memory using multiplexed address and data lines.

Since then, other processors have been developed by INMOS

• T212: A 16-bit version of the T414 with 2K of onboard RAM and a 64K address range. using

separate address and data buses.

• M212: A T212 with two of the four links replaced by a built-in disc controller circuit.

• **T800**: Essentially, a revamped T414 with a floating point coprocessor integrated on the chip,

more instructions, and on-chip RAM increased to 4K. This is one of the more popular transputers sice it combines high performance floating point processing (1.5 MFLOPS)

with the possibilities of parallel processing.

• **T222**: A T212 with 4K of on chip RAM.

• **T425**: An updated T414 with debugging instructions added such as for single stepping.

• **T801**: A T800 with separate address and data lines for faster memory access.

• **T805**: An updated T800 with debugging instructions added such as for single stepping.

When the transputer was first introduced to the market, INMOS essentially forgot to mention the fact that the transputer was actually a microprocessor, different from other microprocessors at the time, but still a microprocessor. For a long time there was also a lack of information on the instruction set and assembly level features of the transputers. In fact INMOS claimed that the transputer was specifically designed to efficiently execute the high level language Occam. They suggested that Occam was the "assembly language" for the transputers. Occam is a high level language with a strong support for parallel processing. The transputer and Occam were jointly developed with each other in mind. As a result Occam programs on the transputer compile to very efficient and tight object code. However, this meant that engineers at that time could not use there beloved FORTRAN programming language. At the same time assembly level programmers could no longer work at the low level. Additionally, there were some things that could absolutely not be done in Occam. A state of anarchy followed, which finally led INMOS to publish "The Compiler Writer's Guide", which gave a detailed explanation of the instruction set for the transputer family.

Transputer multicomputers are appealing for two main reasons. The first one is flexibility, both in the implementation of user-configurable networks, and in a growing software base, which includes, among other languages, C, C++, Occam, Pascal, Modula-2 and Prolog. The second reason is affordability. One-and four-transputer boards are now available for most popular personal computers and workstations, making transputer-based multiprocessors available for as low as \$450 per node, bringing the exploration of parallel programming within the reach of most universities and colleges, and even individuals.

# **Processes And Concurreny in the Transputer**

The transputer uses processes as the basic software building block and provides the direct implementation of a process in hardware. A process is an independent computation (or a sequence of computations) that communicates with other processes. This communication on the transputer is achieved by explicitly defined channels. A process itself may consist of subprocesses by time-sharing.

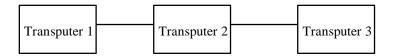

The transputer provides a number of links which support point-to-point communications between transputers, hence allowing processes to be distributed over a network of transputers. Therefore, it is possible to build a system with a network of transputers, with each transputer in the system executing a set of processes and each transputer capable of communicating with others on the network. It should be noted however that each transputer can only communicate directly with another physically connected transputer. It is the ability to specify a hardwired fuction as a process which provides the architectural framework of transputers the capability to be used in highly specialized and diverse applications.

# **Transputer Harware Description**

The transputer is a component designed to exploit the potential of VLSI technology. This technology allows for a large number of identical components to be manufactured cheaply. For this matter it is desirable to be able to implement a concurrent system using identical components. As mentioned earlier the transputer is a high performance microprocessor which has been designed to facilate interprocess and interprocessor communication. The transputer architecture defines a family of programmable VLSI components. The principle features of the transputer architecture are

# A Programmable Device

Transputer systems can be designed and programmed using a variety of different languages including assembly level mnemonics, occam, concurrent Ada, and concurrent versions of C and C++.

### A Multitasking processor with Memory on a single chip

The transputer processor supports multitasking, and enforces two levels of priority for concurrent tasks. Besides allowing the creation of parallel applications where communication and computation functions can be implemented cleanly in separate modules, the multitasking feature provides us with the opportunity to start experimenting with parallelism in a shared memory environment. Almost every operation that a transputer performs involves intefacing with memory. By providing on chip memory this interface time has been greatly reduced.

### Links and channel communication

Transputers communicate with each other via high-speed serial links. The small number of communication wires required and the simplicity of the protocol makes the networking of transputers simple and in most-cases user configurable. This feature allows for the easy evaluation of various network configurations such as rings, meshes, hypercubes, or trees. At the software level, the hardware links are

defined as channels. Hence, while transputers communicate with each other via links, the tasks residing in them communicate through channels. Because the transputer implements communication primitives at its

lowest level (in microcode), and because the access to the serial links is memory-mapped, the transputer offers a powerful feature to the programmer; primitive supporting the communication between tasks residing on different neighboring transputers can also be used to allow tasks residing on the same transputer to communicate. In other words, tasks residing on the same transputer can communicate by sending a message to each other with the same primitive they would use to exchange messages with a task residing on a neighboring transputer. This powerful feature allows the programmer to study first hand some of the complex issues dealing with mapping and folding parallel applications to small networks

### **Virtual Channels**

Virtual channels are a technique for circumventing the limited-fanout of the multicomputer nodes. While a node may be physically limited to four Input/Output links, as is the case for the transputer, a software or hardware routing mechanism can be introduced to allow the transfer of message between different transputers as if they were connected by a channel, even though they may not be directly connected to each other, and their four links may already be connected to other transputers. Hence a virtual path can be created between arbitrary pairs of nodes. This feature, invisible to the programmer, offer a powerful medium for implementing arbitrary networks that can be dynamically configured and modified.

Hence a transputer circuit contains a processor, a small amount of memory, a co-processor, and four high-speed bi-directional links. Although such simple a list may not be impressive, the elegant design of the transputer provides a rich environment for parallel processing.

Worth mentioning is the fact that combining these entities on a single silicon chip was not a technological breakthrough in itself. Other companies, such as Intel or Motorola had introduced versions of their popular 8-bit processors with local memory and interfacing hardware. The novelty was the combination of several factors. One of the most important factor was the introduction of a high-level language, occam whose features were directly supported by the transputer hardware, and that made the transputer a building block for parallel computers. The second prominent factor was the ease with which transputers could be connected to each other with as little as a few electrical wires.

The four bi-directional input/output (I/O) ports of the transputer are designed to interface directly with the ports of other transputers, very much like the pegs on top of Lego blocks fit directly in their bottom cavities. This feature allows for several transputers to fit on a small footprint, with very little extra logic circuits, making it possible to easily fit four transputers with some memory on a PC daughter board (ISA bus), or microchannel board.

#### **IMS T800 Architecture**

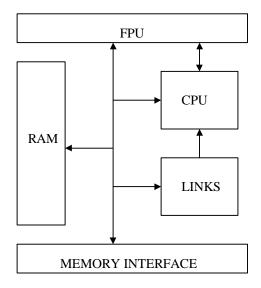

The IMS T800, with its on-chip floating point unit is only 20% larger in area than the T414. This small size and high performance design emerges from a careful note od silicon economics. The IMS T800 architecture is similar to that of the T414. However, in addition to the memory, links, central processing unit (CPU), and the external memory interface, it includes a floating point unit (FPU), which operates concurrently and under the control of the CPU. Figure 1 shows a block diagram for the T800.

The IMS T800, like the T414 operates at two priority levels. The FPU stack is duplicated so that when the T800 switches from low to high, none of the states in the FPU are written to memory. This reduces the worst-case response significantly. Furthermore, duplication of the resgister stack enables the floating-point arithmetic to be used in an interrupt mode

Figure 1

#### **Registers**

The T800 CPU just like the T414, contains three registers (A, B, C) used for integer and address arithmetic, which form a hardware stack. Loading a value into the stack pushes B into C, and A into B before loading A. Storing a value from A pops B into A, and C into B. In addition, there is an operand register that helps in the formation of instruction operands, an Instruction Pointer that points to the next instruction to be executed, and the workspace pointer that points to an area of memory where local variable are held. In addition to these six registers there are four registers theat handle the two active process queues, namely Fptr0, Fptr1, Bptr0, and Bptr1, and two timer registers Time0 and Time1. There are two single bit flags for dealing with erreors, Error and HaltOnError. Also, the first dew locations of memory are used for specific purposes.

Similarly the FPU contains a three register floating-point evaluation stack, consisting of AF, BF, and CF registers. Loading and storing values from the evaluation stack in the FPU functions similar to that of the CPU. The addresses of the floating-point values are formed on the CPU stack, and values are transferred between the addressed memory locations and the FPU stack under the control of the CPU. As the CPU stack is only used to hold addresses of the floating-point values, the word length of the CPU is independent of that of the FPU. Consequently, it would be possible to use the same FPU with a 16-bit transputer such as the T212, for example.

The workspace pointer (W) deserves more attention. It holds an address consisting of a word selector and a byte offset within that word. In the 32-bit transputers two byte offset bits (the least significant two) are used allowing byte offsets of 0, 1, 2 and 3. The byte offset in W is always 0 so that it always points to a word boundary in memory. The least significant bit instead is used to store the process priority, which is 0 for a high priority and 1 for a low priority. This combination of the workspace address and the priority bit is referred to as the process descriptor. A few words of memory just below the workspace pointer are used by various parts of the scheduling hardware as follows (relative to address pointed to by W):

- -1 holds the IP of a descheduled process

- -2 maintain a list of active but descheduled processes.

- -3 Used during channel communication to hold the address of the data to be transferred.

- -4 flag used during timer ALTs to indicate a valid time to wait for.

- -5 used during time ALTS to hold a time to wait for.

### **Communication Links And Protocol**

One of the aims of the transputer architecture is to provide a family of compatible components that can comunicate with each other using minimal amout of external logic, irrespective of the individual internal clock rates. To achieve this, each transputer is equipped with INMOS links, and can communicate using an asynchronous bit-serial protocol. Each transputer has a fixed number of such links, typically four. Each link is bi-directional, and can be used to develop a variety of topologies. Since the communication is asynchronous the relative skew must be kept within tolerance, and is an important consideration while implementing different network topologies.

The messages themselves are transmitted as a sequence of data packets, each of which is acknowledged by an acknowledge packet. Each link consists of a pair of channels, one in each direction. Data packets are multiplexed with acknowledge packets. The acknowledge packets are useful to signal the reception of data, and to maintain smoothe flow control of data. Each data packet consists of two '1' bits followed by eight data bits, followed by one '0' bit. After transmitting a data packet, the sender transputer waits for an acknowledge packet from the receiver. The acknowledge packet consists of one '1' bit followed by one '0' bit.

Communication over both internal and external channels is essentially byte oriented. The only difference as far as software is concerned is that the control word of an external link is at one of the addresses from 0x80000000 to 0x8000001C, rather than an arbitrary address in memory. The same instructions are used for both internal and external channel communication. Hardware determines whether the communication is internal or external, based on the address of the word.

Communications over internal channels observes the following protocol. Before any communication is attempted, the channel word must be initialized to MinInt. This is normally done when the channel is declared and space is reserved for the channel word. When an input or output is subsequently desired, the channel word is inspected. If it is MinInt, the process descriptor of the current process is placed in the channel word, and the process is descheduled. The IP and the address of the data to be transferred are at locations -1 and -3 relative to the workspace pointer, respectively. If however, the channel word was not MinInt, it has to be the process descriptor of some other process, already waiting to communicate, and the communication is performed. Once the data transfer is complete, the process that was descheduled while waiting for communications to commence, is rescheduled, and the channel word is reset to MinInt.

## **Instruction Encoding**

All transputers share the same basic istruction set. It contains a small number of instructions, each with the same format, chosen to give a compact representation of the operations most frequently occuring in programs. Each instruction consists of a single byte divided into two four-bit parts (nibbles); namely function and data. The most significant nibble is the function code. The 16 functions include loads, stores, jumps, and calls. The least significant nibble is the data code.

All instructions place the data code into the least significatant four bits of the operand register (O), left shifting the existing contents four bits. The contents of O are then used as the operand for the function specified by the function code. Instructions normally clear O after they have executed. However a Prefix instruction does nothing after loading the four bits in O. Thus, by using a series of Prefix instructions the range of the data may be extended. A Negative Prfix instruction complements the contents of O after shifting. Finally, an Operate instruction uses its operand as an opcode, giving the transputer access to instructions beyound the basic 16. Since the operand can be extended by prefixing, atransputer may have an arbitrary number of instructions. The only limitaion to this extenibility is that only 13 instructions (the basic ones excluding Prefix, Negative Prefix, and Operate) can have immediate operands. The rest must have implicit operands. For example, the Add instruction adds the contents of A and B together storing the results in A.

The IMS T800 also has additional instructions which load into, operate on, and store from the floating-point register stack. It also has new instructions supporting color graphics, pattern recognition, and implementing error correction codes. It retains the instruction set of the T414. The extension is possible because of the extensible instruction encoding used in transputers.

# **Instruction Set Overview**

This section presents a discussion on the instruction set for the T414. The T414 has 100 instructions which can be grouped as follows:

- 16 addressing and memory acces instructions

- 6 branching and program control

- 41 arithmetic and logical

- 12 process scheduling and control

- 16 inter-process communication

- 9 miscellaneous

### **Addressing and Memory Access Instructions**

There are two ways of addressing memory; namely to specify the address as a fixed offset from the address in the workspace pointer or the A register. Specifying the address as a fixed offset in the workspace pointer is called "local access", since the workspace pointer conventionally points to an area of memory used to hold the local variables for a procedure. Specifying the address as a fixed offset in the A register is called "non-local access".

Instructions are provided for reading and writing bytes or blocks of bytes to and from the memory using the above mentioned addressing schemes

| Instruction | Brief Description                                                                                                                                     |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDL n       | Load Local. Loads a word into Reg A which lies at an offset of n words from the address pointed to by the workspace pointer.                          |

| STL n       | Store Local. Stores a word from Reg A to the memory location which lies at an offset of n words from the address pointed to by the workspace pointer. |

| LDNL n      | Load Non-Local. Loads a word into Reg A which lies at an offset of n words from the address pointed to by the A Register.                             |

| STNL n      | Store Non-Local. Stores a word from Reg A to the memory location which lies at an offset of n words from the address pointed to by the A Register.    |

| LDLP n      | Load Local Address. Loads into the reg A the effective address that is calculated instead of the contents of the address                              |

| LDNLP n     | Load Non-Local Address. Loads into the reg A the effective address that is                                                                            |

|        | calculated instead of the contents of the address                                   |  |

|--------|-------------------------------------------------------------------------------------|--|

| LB     | Load Byte. Loads the byte at the address contained in Reg A into Reg A thus         |  |

|        | overwriting the previous contents of Reg A.                                         |  |

| SB     | Store Byte. Stores the byte contained in the bottom eight bits of Reg B in the      |  |

|        | memory location specified by the address contained in Reg A.                        |  |

| MOVE   | Move Message. Copies a block of bytes from the address in Reg C to the address in   |  |

|        | Reg B. The number of bytes to be moved is specified in Reg A.                       |  |

| WSUB   | Word Subscript. Increments the address in Reg A by the number of words specified    |  |

|        | in Reg B.                                                                           |  |

| BSUB   | Byte Subscript. Increments the address in Reg A by the number of bytes specified in |  |

|        | Reg B.                                                                              |  |

| WCNT   | Word Count. Breaks the address in Reg A into word address and the byte offset       |  |

|        | components, storing them in Regs A and B respectively.                              |  |

| BCNT   | Byte Count. Multiplies the value in Reg A by the number of bytes in a word          |  |

| AJW n  | Adjust Workspace. Increments the workspace pointer by n                             |  |

| GAJW n | General Adjust Workspace. Exchanges the contents of the workspace pointer and       |  |

|        | Reg A.                                                                              |  |

| LDPI   | Load Pointer to Instruction. Calculates an address, which consists of the current   |  |

|        | value of the IP incremented by the contents of Reg A and then stores this value in  |  |

|        | Reg A.                                                                              |  |

|        | i e                                                                                 |  |

**Branching and Program Control Instructions**The transputer provides only has six instructions for altering the flow of control of the program, which brings it close to being a RISC processor.

| Instruction | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CJ n        | Conditional Jump. Examines the contents of Reg A. If the contents are 0 (zero), the IP is incremented by n. The value in A is popped in either case                                                                                                                                                                                                                                                                                                        |  |  |

| Jn          | Jump. Increments the IP by n.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| LEND        | Loop End. Used to implement deterministic loops. Reg A has the displacement which is subtracted from the IP if the instruction succeeds. Reg B has the address of a two word control block. Each time the instruction is executed the contents of the first word are incremented, and the second decremented. If the value in the second word is greater than the first the branch is taken by replacing the contents of IP with (IP - contents of Reg A). |  |  |

| CALL n      | Call. Decrements the workspace pointer by four words, stores the contents of C, B, A and the IP at these memory locations, and then increments IP by n.                                                                                                                                                                                                                                                                                                    |  |  |

| RET         | Return. Loads the IP with the contents of the workspace pointer and increments the workspace pointer by 4 words                                                                                                                                                                                                                                                                                                                                            |  |  |

| GCALL       | General Call. Exchanges the contents of Reg A and the IP                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

# **Arithmetic and Logical Instructions**

| Instruction | Brief Description                                                           |  |  |

|-------------|-----------------------------------------------------------------------------|--|--|

| REV         | Reverse. Swaps the contents of Regs A and B.                                |  |  |

| LDC n       | Load Constant. Loads n in A and pushes the previous contents of Reg A to B, |  |  |

|            | previous contents of B to C, and losing the previous contents of C.                                                                 |  |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MINT       | Minimum Integer. Pushes the constant MinInt onto the evaluation stack.                                                              |  |  |  |

| ADC n      | Add Constant. Adds n to the contents of A.                                                                                          |  |  |  |

| ADD        | Signed Addition. A <= A+B. Error flag is set on overflow                                                                            |  |  |  |

| SUB        | Signed Subtraction.  Signed Subtraction.                                                                                            |  |  |  |

| MUL        | Signed Subtraction.  Multiply.                                                                                                      |  |  |  |

| DIV        | Divide.                                                                                                                             |  |  |  |

| REM        |                                                                                                                                     |  |  |  |

| SUM        | Remainder. Unsigned Addition.                                                                                                       |  |  |  |

| DIFF       | Unsigned Subtraction.                                                                                                               |  |  |  |

| PROD       | Unsigned Multiplication                                                                                                             |  |  |  |

| FMUL       | Fractional Multiply                                                                                                                 |  |  |  |

| EQC n      |                                                                                                                                     |  |  |  |

| EQC II     | Equals Constant. Compares n with the contents of A. If they are equal true (1) is stored in A otherwise a false (0) is stored in A. |  |  |  |

| GT         | Greater Than. If $B > A$ , $A \le true(1)$ else $A \le true(0)$ .                                                                   |  |  |  |

| CSUB0      | Check Subscript from Zero                                                                                                           |  |  |  |

| CCNT1      | Check Count from One                                                                                                                |  |  |  |

| AND        | Bitwise AND                                                                                                                         |  |  |  |

| OR         | Bitwise AND Bitwise OR                                                                                                              |  |  |  |

| XOR        | Bitwise OR Bitwise XOR                                                                                                              |  |  |  |

| NOT        | Complement                                                                                                                          |  |  |  |

| SHL        | 1                                                                                                                                   |  |  |  |

| SHR        | Shift Left                                                                                                                          |  |  |  |

| LADD       | Shift Right                                                                                                                         |  |  |  |

| LSUM       | Long Add                                                                                                                            |  |  |  |

|            | Long Sum                                                                                                                            |  |  |  |

| LSUB       | Long Subtract                                                                                                                       |  |  |  |

| LDIFF      | Long Difference                                                                                                                     |  |  |  |

| LMUL       | Long Multiply                                                                                                                       |  |  |  |

| LDIV       | Long Divide                                                                                                                         |  |  |  |

| LSHL       | Long Shift Left                                                                                                                     |  |  |  |

| LSHR       | Long Shift Right                                                                                                                    |  |  |  |

| XDBLE      | Extend to Double. Converts a single word value into a double word value                                                             |  |  |  |

| CSNGL      | Check Single. Sets the error flag if the value cannot be squeezed into a single                                                     |  |  |  |

| THILODD    | word value.                                                                                                                         |  |  |  |

| XWORD      | Extend to Word                                                                                                                      |  |  |  |

| CWORD      | Check Word                                                                                                                          |  |  |  |

| NORM       | Normalize. Normalizes the double word in BA by shifting it left until the top bit                                                   |  |  |  |

| CFLERR     | is set.  Check Floating Point Infinity or Not A Number (NAN)                                                                        |  |  |  |

| LDINF      | Check Floating Point Infinity or Not A Number (NAN).                                                                                |  |  |  |

|            | Load Single Length Infinity.  Post Normalize Correction.                                                                            |  |  |  |

| POSTNORMSN |                                                                                                                                     |  |  |  |

| ROUNDSN    | Round Single Length Floating Point Number.                                                                                          |  |  |  |

| UNPACKSN   | Unpack Single Length Floating Point Number.                                                                                         |  |  |  |

The last five instructions are not included in the T800 transputer, since it has a floating point coprocessor.

# **Process scheduling and Control Instructions**

The transputer has built in mechanisms to support the concurrent execution of processes. Processes may be operated at two levels of priority. Two queues of active processes are maintained, a high priority process queue and a low priority process queue. A process can be in one of four states: executing, waiting

to execute (it is in one of the active process queues), waiting for a timer event (it is in a timer queue) or waiting for a communication event (it is not in any queue). A high priority process will continue to execute untill it terminates or waits for a timer or communication event to take place. In this case if there are any other high priority processes waiting to be executed, the process from the head of the high priority process queue is scheduled. If there are no high priority processes waiting to execute the next low priority process will be scheduled. A low priority process can be preempted by a high priority process at any time. Low priority processes are time-sliced. If a low priority process executes a loop end (LEND) or a Jump(J) instruction, and it has been executing for more than its time-slice period then it is descheduled and placed at the end of the low priority process queue. The low priority process at the head of the queue will commence execution until the nect time-slice or it is preempted by a high priority process.

| Instruction | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| STARTP      | Start Process. Adds a new process to the back of the active process queue. Reg A holds the address of the workspace that the new process will use, and Reg B holds the offset from IP that the new process will execute. The new process is set at the same priority as the current process, and the current process will continue execution with the nect instruction.                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| ENDP        | End Process. Conditionally terminates the process. It decrements a count in memory. If this count is non-zero it terminates (the next active process is taken and the current process is not added to the end of the queue) otherwise the process continues but at a different execution address and workspace counter. It takes one parameter, an address in Reg A. This address points to the workspace of the parent process At location 0 in this workspace is the restart address for the parent process, location 1 holds the count of the child processes. If this count decrements to zero the workspace pointer is set to the value in the A register, and its IP to the value pointed to by Reg A. |  |  |  |

| STOPP       | Stop Process. Stops the current process. This process is not added back to the end of the queue. The nect active process is scheduled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| STOPERR     | Stop On Error. Same as STOPP, but only if the error flag is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| RUNP        | Run Process. Starts a new process. Reg A has the process descriptor. A process descriptor is the address of the workspace for that process with the bottom bit set to the priority of that process. (A workspace lies on a word boundary making the last few bits unused for address specification). Based on the priority the process is added to the end of the appropriate queue. The IP for that process is set to one word below the workspace address.                                                                                                                                                                                                                                                 |  |  |  |

| STHF        | Store High Priority Front Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| STHB        | Store High Priority Back Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| STLF        | Store Low Priority Front Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| STLB        | Store Low Priority Back Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| SAVEH       | Save Low Priority Queue Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| SAVEL       | Save Low Priority Queue Registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| LDPRI       | Load Priority. Loads 0 or 1 into A based on the priority of the current process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

#### **Inter-Process Communication Instructions**

Inter-Process communication is carried out using channels. A channel is an abstract connection between exactly two processes. One process sends a stream of bytes down the channel to another process, which reads and stores them. If a process tries to send data to another process which is not ready, then the sending process will be descheduled until the receiving process becomes ready, and thus synchronization is achieved.

For two processes running on the same transputer, a channel is implemented by using a word somewhere in memory that is shared by the two processes. This word is referred to as the channel word. Before any communication can take place this word must be inialized to MinInt (Minimum Integer). This with the transputer's signed address space is interpreted as the lowest address in memory. This address can never be the address of a valid workspace. The channel word would normally be initialized by the parent process of two communicating children. When a process tries to communicate, it examines the contents of the channel word. If the contents are MinInt, the other process is not ready, so it stores the process descriptor in the channel word and deschedules. The IP is stored in location -1 of its workspace and the address of the data to be transferred from or to at location -3. When the other process is ready, it examines the contents of the channel word, finds a valid process descriptor and concludes that the other process is ready. It transfers the block of bytes and restarts the other process. All this is implemented within the microcode of the transputer and hence is extremely fast and efficient.

For two processes running on two separate transputers, the two transputers must be connected by hardware INMOS links. Here the communication via channels is taken care of via the hardware within the transputers themselves. When a process on one transputer is ready to send data out to another process on another transputer, the sending process is descheduled. Hardware determines when the other transputer is ready, and transfers the data using Direct Memory Access (DMA), after which the sending process is rescheduled. While this is happening other processes may be executed. At machine code level it appears the same as the former case; the same instructions are used. The distinguishing factor is that in external communication the address of the channel word passes as a parameter in one of the first few locations of memory. The microcode instruction detects the address in one of the reserved locations and pass their parameters on the link hardware for the lik associated with that address.

The proble with the above communication procedures is that the sending process hangs indefinitely until the other process is ready. The transputer also has a suite of instructions, collectively referred to as ALT instructions which allow a series of events to be chosen. The way that ALTs are implemented is described as follows. The first thing that is done is to start the ALT by setting some flags to indicate that an ALT sequence is taking place. Then various guards must be enabled; this is the process of checking channel words used by the guards to see if any of the processes are ready to communicate, finding the earliest time that a timer guard is waiting for and so on. Following this is the wait, which is where the process goes to sleep, until such time that a guard fires. Next, each guard is disabled, and finally, the ALT is ended.

| Instruction | Brief Description                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OUT         | Output Message. Reg A contains the number of bytes to transfer, B points to the channel word, and C points to the start of the data to be sent.                                                                                                                                                                                                                                 |  |  |

| OUTWORD     | Output Word.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| OUTBYTE     | Output Byte.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| IN          | Input Message.                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RESETCH     | Reset Channel. Sets the internal channel word to MinInt or resets the link hardware for an external channel.                                                                                                                                                                                                                                                                    |  |  |

| ALT         | ALT Start. Sets the word at loaction -3 in the workspace to MinInt+1. This indicates that no guards have been fired yet. This location also corresponds to the location where the data address is stored in an IN or OUT instruction. This means that another process will be able to tell that the process is an ALT process because MinInt can never be a valid date address. |  |  |

| TALT        | Timer ALT Start. Does everything that ALT does and then sets location -4 to MinInt+2, indicating that no valid time has yet been stored.                                                                                                                                                                                                                                        |  |  |

| ENBC        | Enable Channel.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| ENBS        | Enable Skip.                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| ENBT        | Enable Timer.                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| ALTWT       | ALT Wait.                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| TALTWT | Timer ALT Wait.                                                        |  |

|--------|------------------------------------------------------------------------|--|

| DISC   | Disable Channel.                                                       |  |

| DISS   | Disable Skip.                                                          |  |

| DIST   | Disabel Timer.                                                         |  |

| ALTEND | ALT End. Performs a relative jump based on the contents of location 0. |  |

### **Miscellaneous Instructions**

| Instruction | Brief Description                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| STTIMER     | Store Timer. Sets the values of the low and high priority timer registers to the value in Reg A.                                                                                                                                                                                                                                                                                                       |  |  |

| LDTIMER     | Load Timer. Pushes the value of the current priority timer register into Reg A.                                                                                                                                                                                                                                                                                                                        |  |  |

| TIN         | Timer Input. Suspends the current process until the time in the current timer register is after the value specified in Reg A. Other processes may execute in the mean time. The current process in inserted into a timer list of sorted processes. Each time the timer register is incremented it is checked against the process at the head of the list, and if necsssary the process is reactivated. |  |  |

| SETERR      | Set Error Flag.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TESTERR     | Test Error Flag. A<= false(0) if the error flag is set.                                                                                                                                                                                                                                                                                                                                                |  |  |

| CLRHALTERR  | Clear Halt on Error Flag.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| SETHALTERR  | Set Halt on Error Flag.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| TESTHALTERR | Test Halt on Error Flag.                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| TESTPRANAL  | Test Processor Analyzing.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

# **Example Assembly Level Program**

**Example :** Implement the following C code for( i=3; I<=8; I++) j=j+i;

**Solution:**

|     | LDC   | 3;       | line 1  |

|-----|-------|----------|---------|

|     | STL   | block;   | line 2  |

|     | LDC   | 8+3-1;   | line 3  |

|     | STL   | block+1; | line 4  |

| L1: | LDL   | j;       | line 5  |

|     | LDL   | block;   | line 6  |

|     | ADD;  |          | line 7  |

|     | STL   | j;       | line 8  |

|     | LDC   | L2-L1;   | line 9  |

|     | LEND; |          | line 10 |

| L2: |       |          |         |

In line 1, the value 3 is loaded into Reg A, line 2 stores this value from Reg A to the memory location at an offset of "block" from the address pointed to by the workspace pointer.

In line 3, the value 8+3-1=10, is stored in Reg A, pushing the previous value from Reg A (3) into Reg B.

Once again in line 4, the value from Reg A is stored in the memory location at an offset of "block+1" from the address pointed to by the workspace pointer. Reg A once agian holds 3 now. Lines 1 through 4 makes up the control block

In line 5, the value in the memory location at an offset of "j" from the address pointed to by the workspace pointer is loaded in Reg A, pushing the previous contents of B to C, and A to B. In line 6, the value in the memory location at an offset of "block" from the address pointed to by the workspace pointer is loaded in Reg A, pushing the previous contents of B to C, and A to B. At this point Reg C has the offset of the control block relative to the workspace pointer.

Line 7 adds the contents of Reg A and B (i+j) and stores the result in Reg A.

Line 8 stores this value in Reg A in is stored in the memory location at an offset of "j" from the address pointed to by the workspace pointer. Also, the contents of B are popped into A. Line 9 loads A with the displacement.

Line 10 is very critical. At this point Reg A contains the displacement, and Reg B contains the control block (block, and block+1). The contents of "block" are incremented by one, and the contents of "block+1" are decremented by one. As long as the contents of "block" are less than that in "block+1" the contents of Reg A are subtracted from the IP, and the loop is taken.

12

# OCCAM: THE NATIVE LANGUAGE

# **Introduction**

Occam is an abstract programming language whose development has been closely associated with that of the transputer. (Both have been designed by INMOS). Although linked with the transputer, the importance of occam goes beyond its implementation on any hardware system. It is a result of many years of research, and is a concurrent programming language that is simple, elegant and powerful.

The name occam was chosen in recognition of its simplicity. Wiiliam of Occam, a 14th century philosopher said "Entities are not to be multiplied beyond necessity", which is a plea to keep things simple.

# **InterProcess Communication in Occam**

Occam uses a single straightforward structure that encompasses both ease of programming, and ease of implementation. A synchronous communication method was chosen that combines in a single primitive, the needs of data communication and synchronization. The communication is built on the use of what is called a channel. Two factors have in particular influenced this.

- Occam incorporates an exhaustive view of concurrency; programs consist of a large number of processes and it would be inconvenient to name them all. Indirect naming allows processes to be anonymous.

- 2. Modifications to occam programs are easier to accommodate if the communication between processes takes place via an explicitly defined intermediary.

The channel is unidirectional and can only be used by one calling process and one called process. Other characteristics of the channel have also been influenced by the need to associate a channel with a link between adjacent transputers. The commands for writing to and reading from have a simple and terse format. Let 'ch' be the channel. Then the command to write to this channel, the value contained in the variable X, would be :

ch!X

The symbol! indicates output.

Similarly, to read the channel and store the results in the variable X, the command (from another process) would be :

ch?X

The symbol? indicates input

The first process to execute one of these commands is suspended until the other process catches up. Both processes will then proceed, independently and concurrently.

### **Deadlocks And Indefinite Postponements**

Deadlock is a situation that occurs when two or more processes are waiting on each other and it is impossible for any one of them to proceed without external arbitration.

Consider two occam processes P1 and P2 wishing to exchange some data. Let chan1 and chan2 be the two channels.

P1: chan1! A chan2? B

P2: chan1? X chan2! Y

The above code will work correctly under all circumstances. However, if the two statements in process P2 are reversed

P2: chan2! Y chan1? X

both processes P1 and P2 will be suspended indefinitely. P1 can not proceed until P2 has read from chan1, and P2 can not proceed until P1 has read from chan2. Predicting deadlocks is not easy, and they sometimes occur rarely, but with devastating results.

A less severe, though still significant, condition is that of indefinite postponement (also referred to as lockout or starvation). This may occur, for example, when a low priority process tries to access a busy resource. Even if the postponement is not indefinite, but merely indeterminate, the program behaviour may be unpredicatable. It is very important that the run-time system implementing the concurrent execution of the processes implements a fair scheduling algorithm, such as the first-in first-out (FIFO) queue or a round-robin algorithm.

# **Occam Processes**

The basic model for an occam program is a network of communicating processes. Communication is defined via channels with each process within the program performing a sequence of actions which may proceed indefinitely. A process may also contain other processes so that a heirarchical structure is supported. At the top level the entire occam program is a single process.

An occam process can be of one of the following types.

- Primitive Process

- Block

- Constructor

- Procedure Instance

#### **Primitive Processes**

Occam supports five primitive processes: STOP, SKIP, assignment, input, and output.

- STOP is a process that has no action but which never terminates. Its effect is to therefore inhibit any parent process from continuing. It is quite drastic, and mostly only executed in response to some error condition.

- SKIP is the inverse of the STOP process although it has no effect. SKIP is always ready to execute and terminates immediately. It is a null process.

• An assignment has the form

v := e

where v is the variable, and e is the expression of the same type. An assignment process will normally terminate immediately, unless an error occurs and a STOP process is executed.

• A novel feature of occam is that communication is viewed at the same level as assignment. As mentioned in the previous section, ch! e, is an output and, ch? x, is an input.

### **Blocks and Channels**

A block process is a specification followed by a process. Blocks may be contained within other blocks, and the usual scope rules apply. There are three types of channels; namely input, output and timer channels.

• Input and output channels are declared using the CHAN keyword as follows:

[Number] CHAN OF <Protocol type> <channel name list>: where, Number is only required to declare an array of channels Protocol type specifies the channel protocol channel name list is the list of channel names.

• Timer channels are declared as follows:

Timer < list of names>:

A timer channel has the characteristic that its always ready to output. Obviously, only read actions on timers are allowed.

### **Constructors**

Constructors provide the glue for putting together the primitive processes. Five distinct constructors are provided: SEQ, WHILE, IF, PAR, and ALT. With each of these a replicator may be attached (except in WHILE) to give an extra dimension.

- SEQ provides for sequential execution of a collection of processes. The collection may be of any size.

- To execute a sequence a number of times, the WHILE construct is used. The sequence is executed as long as the expression in the WHILE construct evaluates to TRUE.

This code executes as long as A < 32 or A > -32.

A replicator is used to duplicate a component process a number of times, just like a for loop in many other high level languages.

```

eg. SEQ I= 0 FOR 10

CNT! I

```

transmits integers 0 through 9

A replicator can only be applied to a single subprocess. To execute a collection of subprocesses, they must be wrapped into a SEQ process.

• Occam provides conditional branching based on the IF construct.

```

eg. IF X < 0 Y := -1 X > 0 Y := 1

```

- In order to indicate that two or more processes ar concurrent the PAR construct is used. All subprocesses of PAR must be completely independent or interact using channels. From a program execution standpoint PAR has two main uses

- 1. To express concurrency, or to indicate candidates for true parallel execution.

- 2. To introduce non determinacy into the program

PAR itself is a process, and terminates when and only when all of its constituent subprocesses terminate. PAR can also be used in conjunction with a replicator when a number of similar processes are to be generated.

```

eg. VAL INT N IS 10

[N+1]CHAN OF INT C:

PAR

PAR P= 0 FOR N

INT BufferElement:

WHILE TRUE

SEQ

C[P] ? BufferElement

C[P+1]! BufferElement

```

eg. If P(I) and Q(I) are two occam processes whose actions depend on the value of I then the following code :

PAR P(1) P(2) P(3) Q(1) Q(2) Q(3)

could be written more concisely as

```

\begin{aligned} \text{PAR I} &= 1 \text{ FOR 3} \\ \text{PAR} & \\ \text{P(I)} \\ \text{Q(I)} \end{aligned}

```

When a PAR process is executed, a number of subprocesses are created. With a replicated PAR process the number of subprocesses created is determined by the number of replications. Each of these subprocess in turn may create a number of other subprocesses. Occam, however does not allow dynamic process creation, and hence the number of processes and subprocesses under each one of these processes must be known at compile time. This restriction is made to allow occam to

determine memory allocations and calculate queue lengths. Therefore the second field of a replicator used with a PAR is restricted to an expression that can be calculated at compile time. Consider the code fragment

```

SEQ

NumProcesses ? N

PAR I = 1 FOR N

SubProcess(I)

```

This is not allowed.

However, the above code fragment can be re-written as follows

```

VAL INT MAX IS 100

NumProcesses ? N

SEQ

IF

N > 100

SKIP

PAR I = 1 TO MAX

IF

I <= N

SubProcess(I)

TRUE

SKIP

```

Here, the maximum number of processes (MAX) is always generated. However, all processes greater than the number of processes required are merely SKIP processes, which terminate immediately.

The PAR constructor also allows the concurrent processes generated to have different priorities. The priority of a process determines how much relative processing time the process gets. The higher the priority of a process, the more processing time it gets.

```

eg. PRI PAR

P1

PAR

P2

P3

P4

```

In order to assign priority to the concurrent processes, a variant of PAR, PRI PAR must be used. As in the example P1 has highest priority, P5 has lowest priority, and processes P2, P3 and P4 have a priority in between those of P1 and P5. The priorities are assigned from highest to lowest to the processes in the order in which they appear.

Once a program has been designed, developed, and verified; its final execution may be assigned to a neumber of processors. Another variant of the PAR constructor is used for this purpose. The PLACED PAR indicates that the associated subprocesses are not only concurrent, but they are to alloted to different processors, and hence will be truly parallel.

```

eg. PLACED PAR

PROCESSOR 1

P1

PROCESSOR 2

P2

```

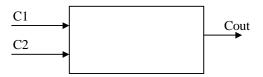

• The ALT constructor allows a flexible construct of selecting one process of various alternative processes.

```

INT X:

WHILE TRUE

ALT

C1 ? X

Cout! X

C2 ? X

Cout! X

```

For each execution of ALT one, and only one, of the alternatives is selected. The selection of the alternative is based on a guard condition. When a guard condition is ready, the process associated with it is executed. If no guard is ready, the ALT process is suspended until there is one.

```

eg. TIMER Clock:

CHAN OF INT IS Input

INT time, X:

SEQ

Clock? time

ALT

Input? X

-- Normal Action

Clock? AFTER time PLUS 1000

-- Timeout Action

```

Depending on which guard condition gets ready first, normal action or timeout action is taken.

Like the PAR construct, a replicator may be used with the ALT construct.

If more than one guard condition becomes ready at the same time, the one chosen for execution is not defined in the language. Hence a variant of the ALT, PRI ALT is provided, which prioritizes the guard conditions. Once again, priorities to the guard conditions are assigned the same way as in the PRI PAR construct; the one textually first gets the highest priority and so on.

# **Channel Protocols**

In order to avoid run-time errors, and also, to make channel communications more efficient, occam has added protocols to the definition of the language. Once a channel is defined, both input and output operations must be compatible with the defined protocol. A protocol is a statement about the type of object using the channel.

# **Simple Protocols**

A simple protocol is used to pass a single object, or a variable array down a channel. A simple protocol need not be explicitly defined; it can be used directly in the definition of the channel.

## **Simple protocol for Primitive types**

A primitive protocol is merely a simple scaler type, for example, an integer.

```

eg. CHAN OF INT C1:

```

The operation C1! X or C1? X is compatible with the protocol as long as X is of type INT.

# Simple protocol for Fixed Length Array types

An array is a group of elements all of the same type. For example, in order to communicate an array of five integers the following code fragment may be used

```

CHAN OF [5]INT C5:

PAR

[5]INT OUT :

SEQ

C5 ! OUT

[5]INT IN :

SEQ

C5 ? IN

```

Another variant of the code would be, for example,

```

CHAN OF [5]INT C5:

PAR

INT OUT1, OUT2, OUT3, OUT4, OUT5:

SEQ

C5 ! [OUT1, OUT2, OUT3, OUT4, OUT5]

INT IN1, IN2, IN3, IN4, IN5:

SEQ

C5 ? [IN1, IN2, IN3, IN4, IN5]

```

In both the above code fragments, the usage of the channel is compatible with the protocol since each time five integer variables are used.

### Simple protocol for Variable Length Array types

This is a more general type protocol than the previous one. The usage is as follows CHAN OF BYTE::[]INT C256:

The above declaration would allow upto 256 integer values (BYTE is a one byte location) to be sent or received over C256.

```

eg. C256! 7::[23,24,56,34,1,2,567]

C256! 17::[A FROM 6 FOR 23] where A is an array of atleast 23 integers.

C256? num::[B FROM 0 FOR num]

```

In each of the above three examples, the first value (in this case of type BYTE) is the number of data elements (in this case type INTs) to be transferred, and then the actual data follows.

# Simple protocol for Record types

Records are a collection of elements of different types, which are grouped together as a single entity. For example, a student record may contain is name, major, and grade.

```

eg. RECORD IntAndByte IS (INT,BYTE):

CHAN OF IntAndByte Crec:

PAR

IntAndByte IBRec:

INT I:

BYTE B:

SEQ

Crec! IBRec

Crec? (I,B)

Crec! (45,'A')

```

# **Sequential Protocols**

Arrays and Records can be used to communicate groups of objects down channels as single logical transactions. A sequential protocol allows such groups to be communicated without the use of such structured types. A sequential protocols gives the type of each object being transferred.

eg. C! x1;x2;x3;x4 is compatible with the protocol P1;P2;P3;P4 as long as x1 is xompatible with P1.and so on.

A sequential protocol must be defined before it can be used

```

eg. PROTOCOL FiveInt IS INT;INT;INT;INT: CHAN OF FiveInt C5:

PAR

ch! 2,45,3345,23,5678

ch? in1,in2,in3,in4,in5

```

### **Variant Protocols**

What if two processes wished to pass data of different types and in no particular order? While solutions exist using simple and sequential protocols, they are too expensive in terms of the number of channels used and in the possibility of a deadlock situation arising. Variant protocols come to the rescue.

```

eg. PROTOCOL INT.OR.REAL

CASE

Fixed; INT

Float; REAL32

:

CHAN OF INT.OR.REAL C.all

PAR

SEQ

C.all! Fixed; I

C.all! Float; R

SEQ

C.all? CASE

```

Fixed; J Float: X

# **ANY Protocols**

If the channels is defined to have a protocol ANY, then all possible uses of the channel are legal, and the compiler does not perform any type checking. The use of ANY protocol must be very restricted and with great care.

# **Occam Input And Output**

# **High Level Input And Outut**

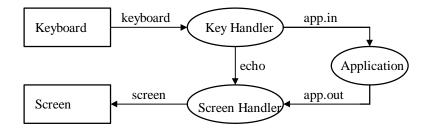

The basic model for I/O in occam for channels to pass data between the program and the program's environment. A typical program would therefore have many internal channels and a few external ones. The external channels would be half inside the program and half outside the program. Such channels are specified by explicitly allocating the channel

```

eg. CHAN OF INT C:

PLACE C AT X:

where X is an implementation dependent constant.

```